# Logique séquentielle

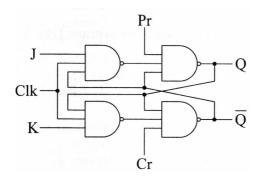

### I Bascule J-K

- 1. Montrer qu'une Remise à Un (RAU : Cr=1 et Pr=0) de la bascule J-K ne peut se faire correctement que si  $\overline{K} + \overline{C1k} = 1$

- 2. Montrer qu'une Remise à Zéro (RAZ : Cr=0 et Pr=1) de la bascule J-K ne peut se faire correctement que si  $\overline{J} + \overline{Clk} = 1$

- 3. Qu'en concluez vous sur l'usage des entrées asynchrones

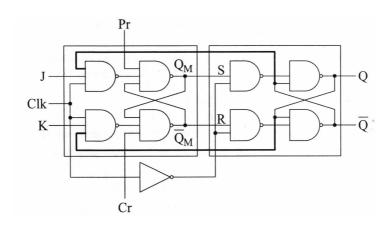

#### II Bascule J-K maître-esclave

Nous considérons une bascule J-K maître-esclave dans l'état initial Q=0 et  $\bar{Q}=1$

- 1. Que devient Q<sub>M</sub> lorsque Clk=1, J=0, K étant dans un état quelconque?

- 2. Que devient Q<sub>M</sub> si J passe dans l'état 1?

- 3. Que devient  $Q_M$  si J revient dans l'état 0? Qu'en concluez vous ?

# III Bascule J-K maître-esclave

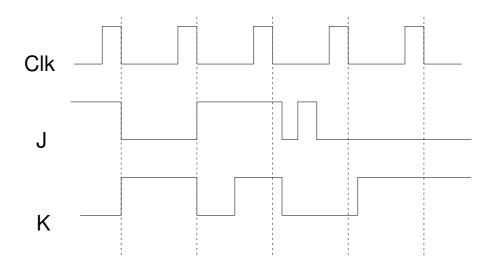

La figure suivante donne le chronogramme des signaux appliqués aux entrées J, K et Clk d'une bascule J-K maître-esclave. En supposant que la bascule est dans l'état Q=0 avant l'arrivée du premier signal d'horloge, tracer le chronogramme des sorties Q et  $\bar{Q}$  (les entrées asynchrones sont dans l'état Pr = Cr = 1)

#### **IV** Bascules

- 2. Vérifier qu'une bascule de type D devient une bascule de type T si D est connectée à  $\bar{Q}$

#### V Réalisation d'une bascule

Montrer comment réaliser une bascule A-B dont la table de vérité est donnée ci-dessous, en utilisant une bascule J-K et toute la logique nécessaire

| An | B <sub>n</sub> | $Q_{n+1}$                            |  |

|----|----------------|--------------------------------------|--|

| 0  | 0              | $\overline{\mathbf{Q}_{\mathrm{n}}}$ |  |

| 1  | 0              | Qn                                   |  |

| 0  | 1              | 1                                    |  |

| 1  | 1              | 0                                    |  |

ESIL Département d'Informatique Année 2006-07 TD d'Architecture : Logique séquentielle

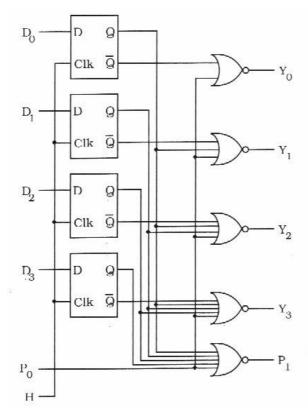

# VI Registre prioritaire cascadable

Le schéma suivant représente un registre prioritaire cascadable de 4 bits

- 1. Posons :  $P_0 = 0$ ,  $D_0 = D_1 = D_3 = 0$  et  $D_2 = 1$ . Vérifier que  $Y_2 = 1$  et que toutes les autres sorties sont à 0.

- 2. Posons :  $P_0 = 0$ ,  $D_0 = D_1 = 0$  et  $D_2 = D_3 = 1$ . Vérifier que  $Y_2 = 1$  et que toutes les autres sorties sont à 0.

- 3. Généraliser les résultats précédents en montrant qu'une seule ligne de sortie  $Y_i$  peut être dans l'état 1, celle ci corespondant à l'entrée  $D_i$  de plus bas poids dans l'état 1.

- 4. Comment cascader deux circuits de ce type pour obtenir un registre prioritaire de 8 bits ?

# VII Etude d'un compteur

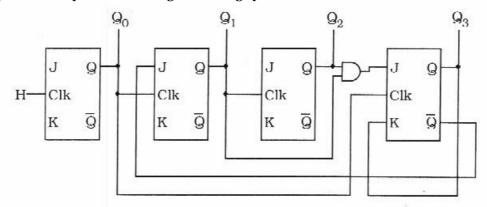

Soit le compteur correspondant au diagramme logique suivant :

- 1. Ecrire la table de vérité des sorties Q<sub>0</sub>, Q<sub>1</sub>, Q<sub>2</sub> et Q<sub>3</sub>, en partant de 0000 après chaque impulsion d'horloge. Quand aucune connexion n'est visible, il faut comprendre que l'entrée correspondante est toujours dans l'état 1. Vérifier qu'il s'agit d'un compteur modulo 10.

- 2. Comment peut-on utiliser ce système en compteur modulo 5 ?

### VIII Etude d'un compteur

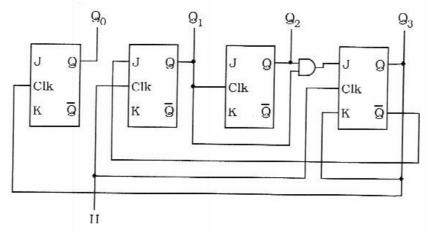

Soit le compteur asynchrone correspondant au diagramme logique suivant :

- 1. Ecrire la table de vérité des sorties Q<sub>0</sub>, Q<sub>1</sub>, Q<sub>2</sub> et Q<sub>3</sub>, en partant de 0000 après chaque impulsion d'horloge. Quand aucune connexion n'est visible, il faut comprendre que l'entrée correspondante est toujours dans l'état 1. Vérifier qu'il s'agit d'un compteur modulo 10.

- 2. Ce compteur est dit biquinaire' (deux f ois cinq) car la sortie Q<sub>0</sub> ne change d'état que toutes les 5 impulsions. Votre table de vérité doit vérifier cette dénomination.

# IX Etude d'un compteur

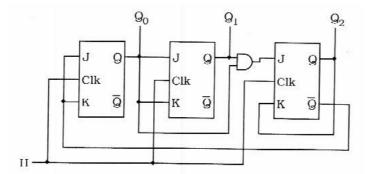

Soit le compteur synchrone correspondant au diagramme logique suivant :

- 1. Ecrire la table de vérité des sorties Q<sub>0</sub>, Q<sub>1</sub> et Q<sub>2</sub> en partant de 000 à chaque impulsion de l'horloge.

- 2. A quoi correspond ce compteur?

#### X Etude d'un compteur

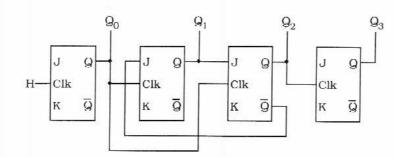

Soit le compteur asynchrone correspondant au diagramme logique suivant :

- 1. Ecrire, en la justifiant, la table de vérité des sorties Q<sub>0</sub>, Q<sub>1</sub>, Q<sub>2</sub> et Q<sub>3</sub> en partant de 0000 après chaque top d'horloge. De quel type de compteur s'agit-il ?

- 2. Comment peut-on utiliser ce système en compteur modulo 6?

#### XI Etude d'un compteur

Soit le compteur réalisé avec des bascule T de type maître-esclave correspondant au diagramme logique suivant

- 1. Pour chacune des bascules, exprimer l'état des entrées asynchrones  $\text{Pr}_i$  et  $\text{Cr}_i$  en fonction des entrées LOAD et  $\text{E}_i$

- Compléter la table de vérité suivante

ESIL Département d'Informatique Année 2006-07 TD d'Architecture : Logique séquentielle

| LOAD | Ei | Pr <sub>i</sub> | Cr <sub>i</sub> | $Q_{i}$ |

|------|----|-----------------|-----------------|---------|

| 0    | 0  |                 |                 |         |

| 0    | 1  |                 |                 |         |

| 1    | 0  |                 |                 |         |

| 1    | 1  |                 |                 |         |

Quelle est la fonctionnalité associée à l'entrée LOAD ? Dans quel état doit-elle être en fonctionnement normal du compteur ?

- 2. Donner l'epression logique de l'entrée T<sub>i</sub> de chacune de ces bascules

- 3. Quel est l'état de chacune de ces entrées T<sub>i</sub> lorsque l'entrée ENABLE du compteur est dans l'état 1 ? Qu e peut-on en conclure sur la fonctionnalité de cette entrée ENABLE ? Dans quel état doit-elle être en fonctionnement normal du compteur ?

- 4. En mode de fonctionnement normal, sur quelles transitions du signal d'horloge H se font les changements d'état du compteur ?

- 5. Lorsque l'entrée U/D est dans l'état 1," donne r la table des transitions du compteur en supposant chaque bascule initialement dans l'état 0."D e quel type de compteur s'agit-il?

- 6. Même question quand l'entrée U/D est dans l'état 0." En déduire la fonctionnali té de l'entrée U/D.

- 7. Donner l'expression logique de la sortie MaxMin. Pour quelles valeurs du compteur cette sortie est-elle dans l'état 1''? En déduire son intérêt.